...in 2050

José A. Cobos

April 1st, 2023

**Three Corners Power Electronics

Extended Collaboration

(3C-PEEC) Workshop**

*Moving Towards a Carbon-Free

World by 2050*

## #1 Adoption of VA area models

Reconfigure SOURCE, LOAD & power architecture

...in 2050

Process LESS

Process BETTER

## #2 Use HV devices in LV applications

"i" impacts more than "v" on conduction loss

## #3 SURFACE power delivery

Generate LOAD current ubiquitously

(Extension of "Point of Load")

José A. Cobos

April 1st, 2023

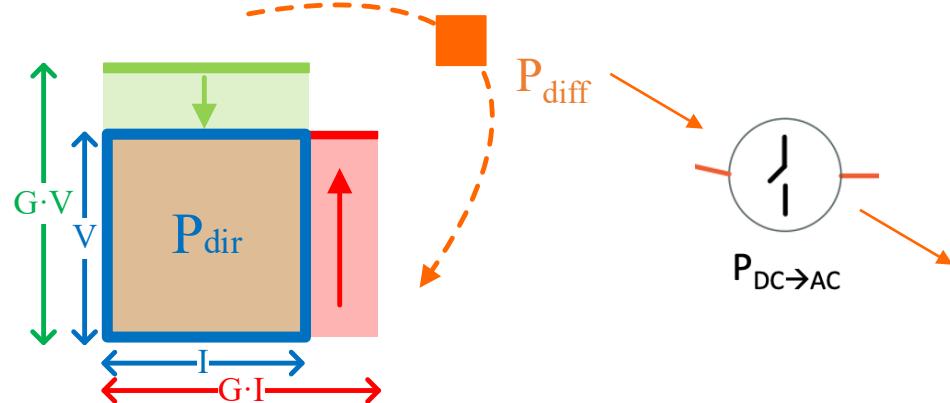

# #1 Adoption of VA area models

Reconfigure SOURCE, LOAD & power architecture

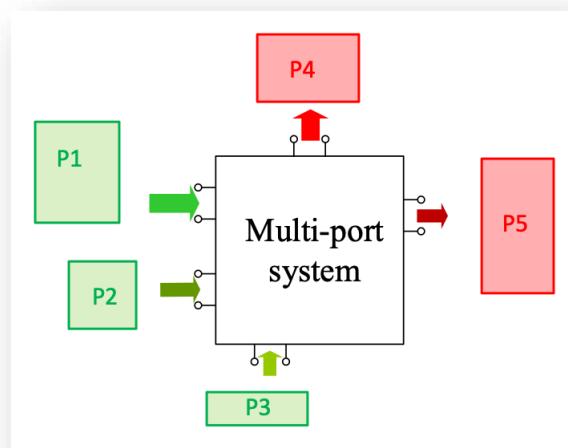

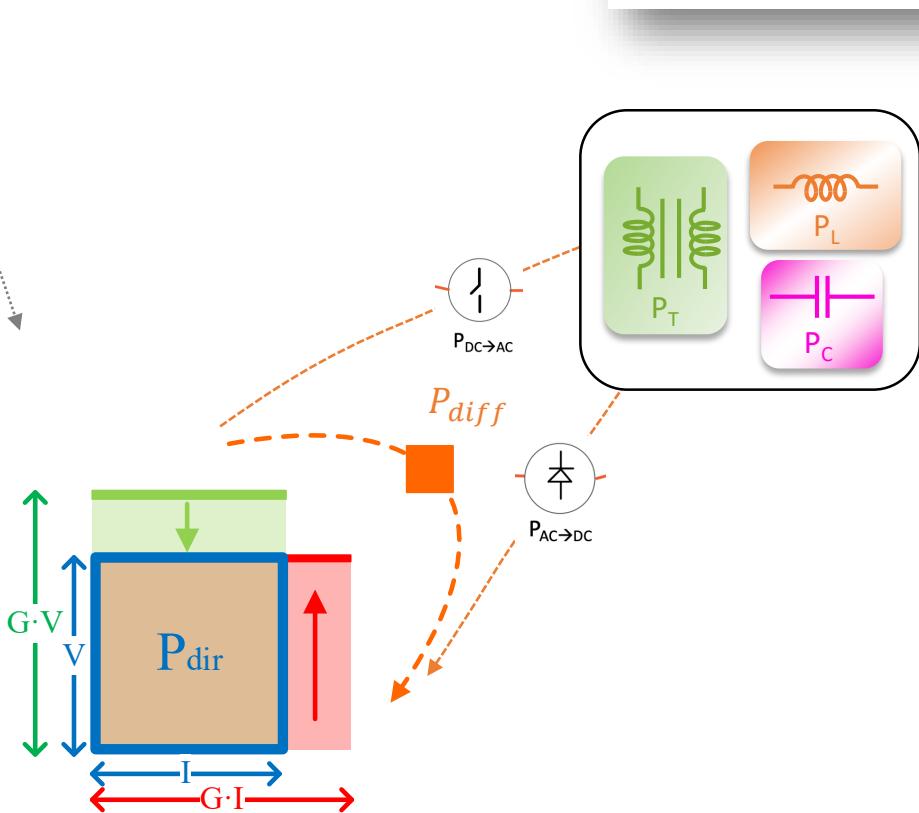

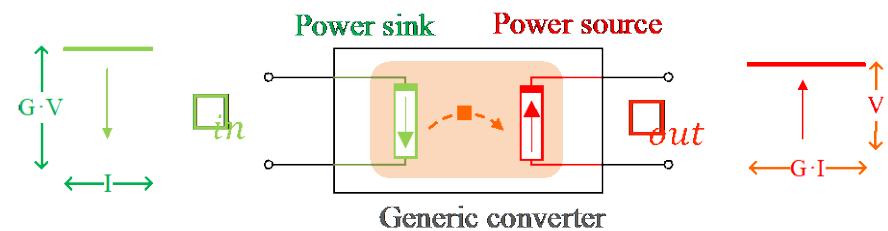

**"Processed"** Power, instead of

**"supplied"** power, is calculated

to SYNTHESIZE Power converters

&

RECONFIGURE sources & Loads

# #1 Adoption of VA area models

Reconfigure SOURCE, LOAD & power architecture

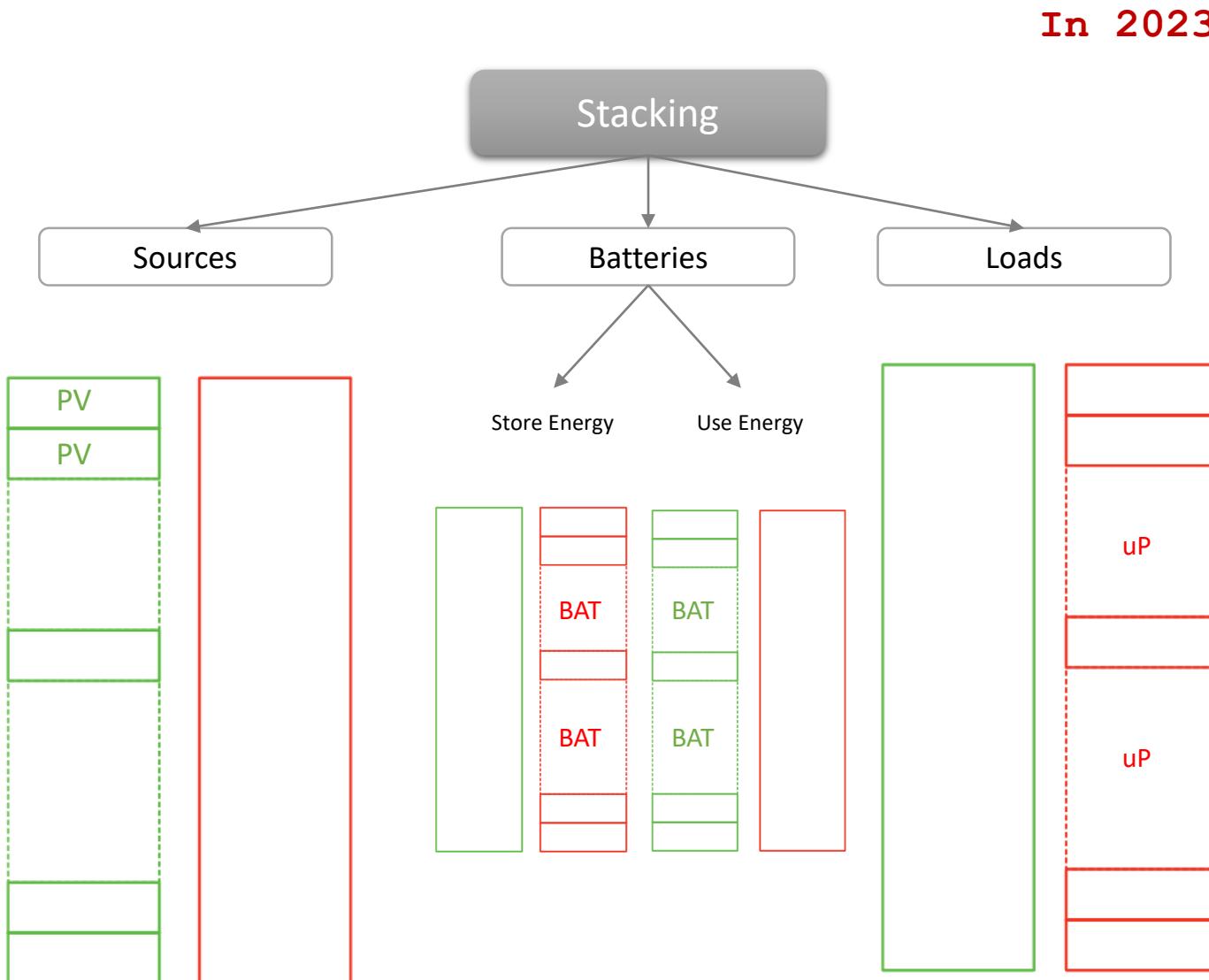

In 2023...

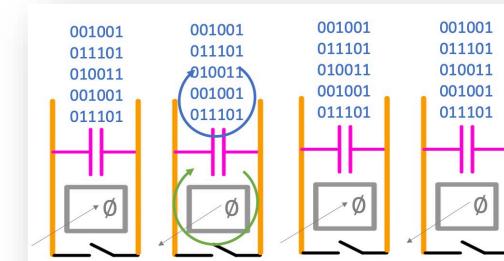

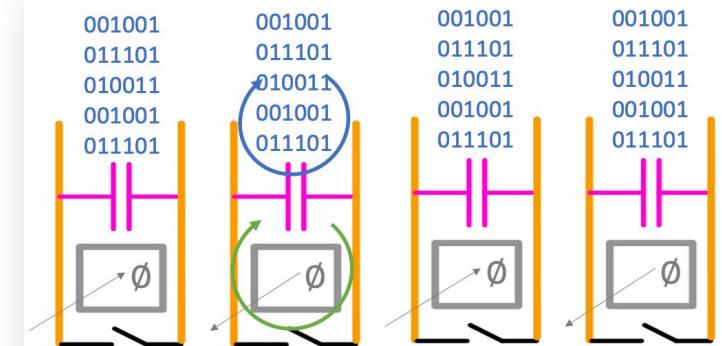

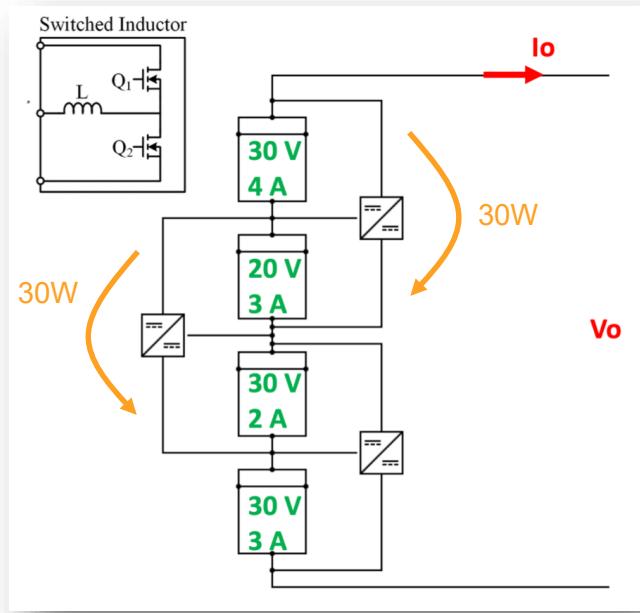

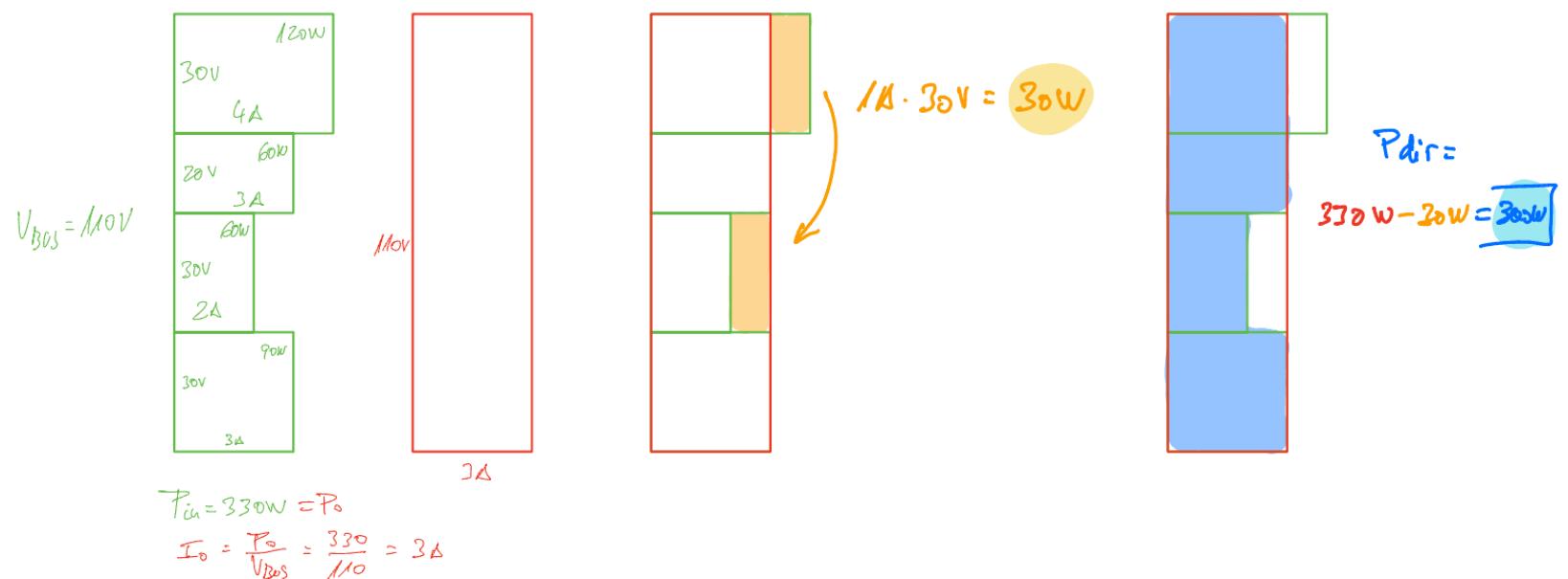

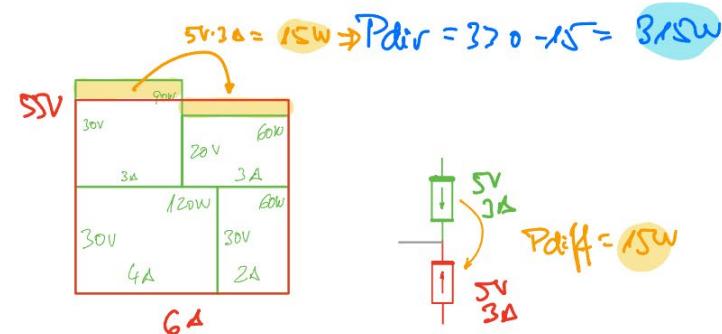

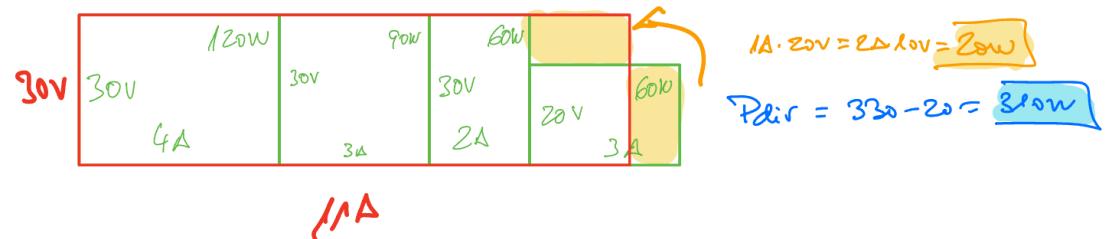

## Stacking (DPP)

## 60W “processed”

330W “supplied”

What is the minimal power to be processed?

30W “processed” !!

...in 2050

## Student quiz at UPM

## #1 Adoption of VA area models

Reconfigure SOURCE, LOAD & power architecture

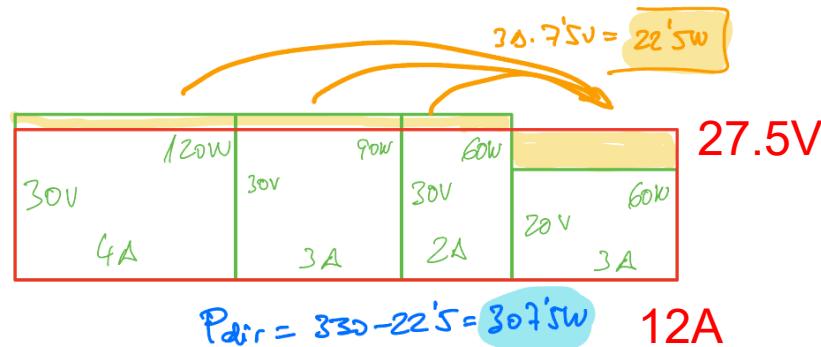

### Reconfigurability

22.5W "processed" !!

20W "processed" !!

15W "processed" !!

75% less power processing

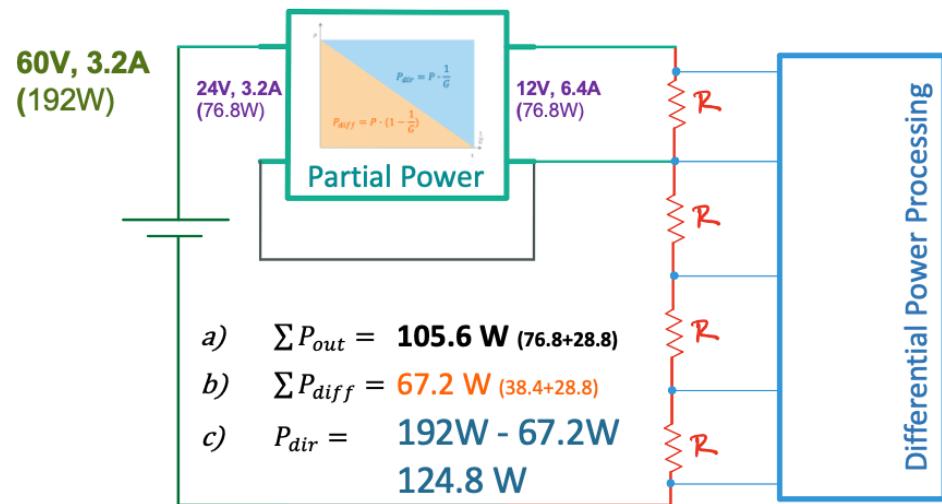

In 2023...

"supplied" power is used for optimization

40% less power processing

...in 2050

"processed" power is used for optimization

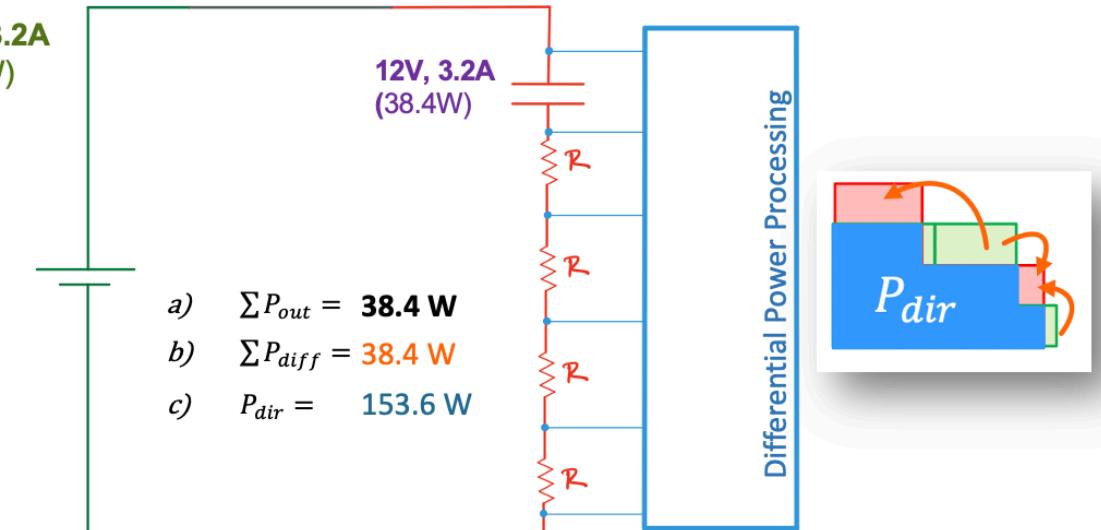

DPP+ 67.2W

38.4W DPP

Partial Power

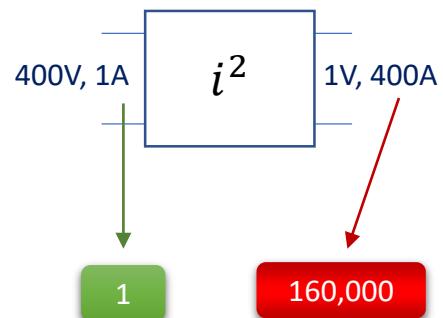

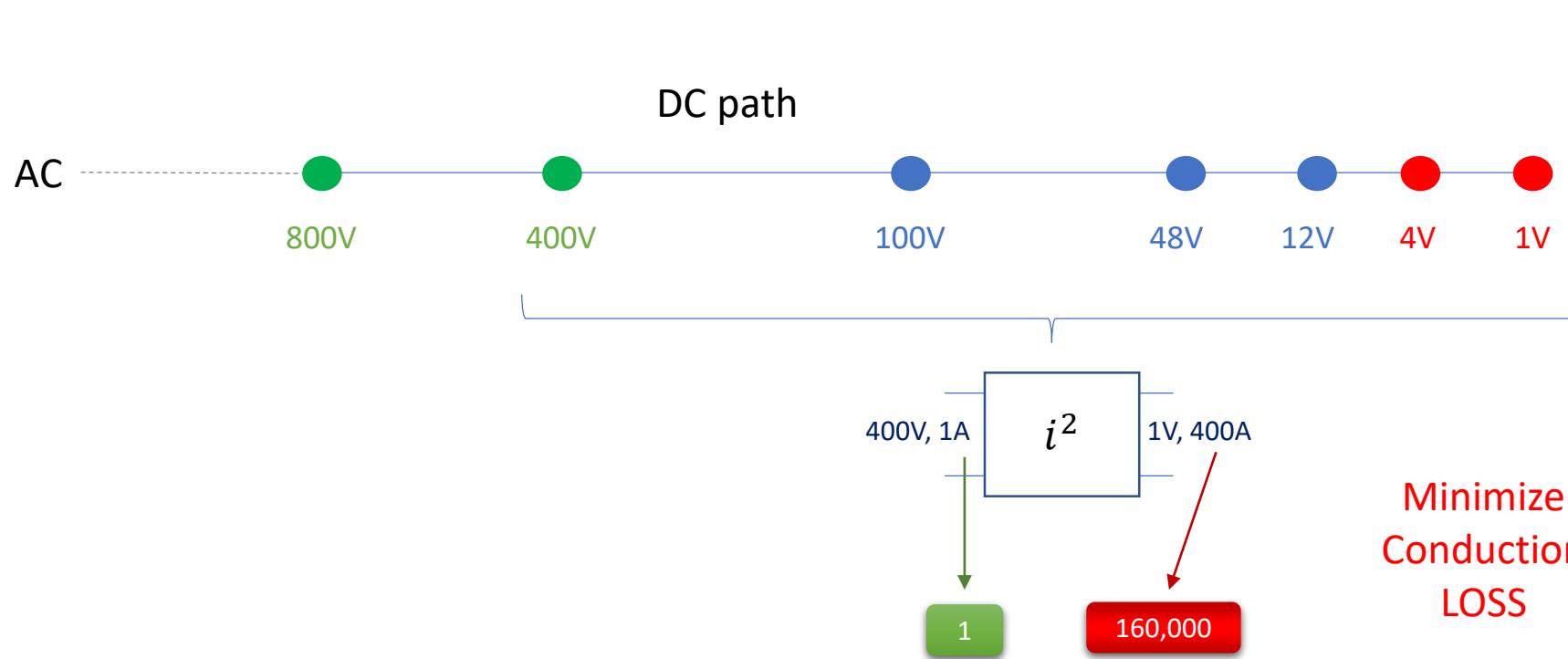

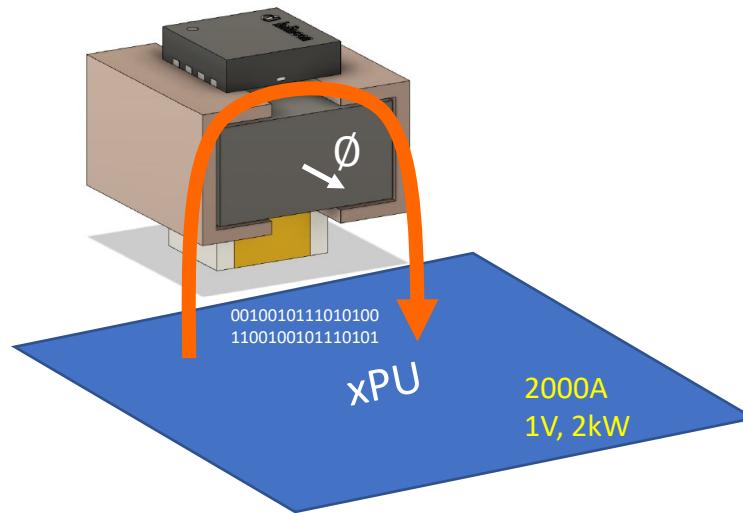

## #2 Use HV devices in LV applications

“i” impacts more than “v” on conduction loss

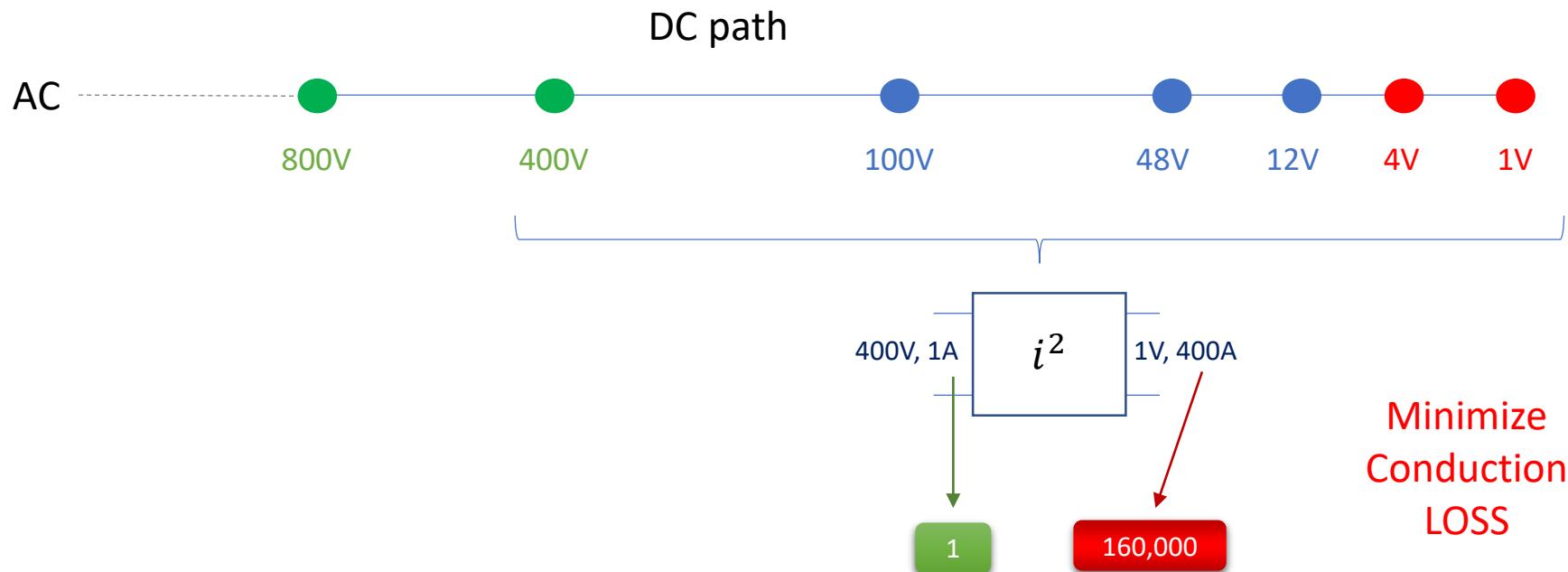

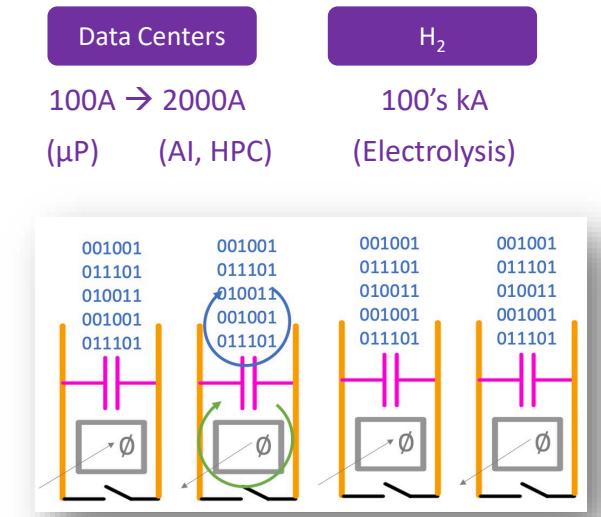

Data Centers

100A → 2000A

(μP)

H<sub>2</sub>

100's kA

(AI, HPC)

(Electrolysis)

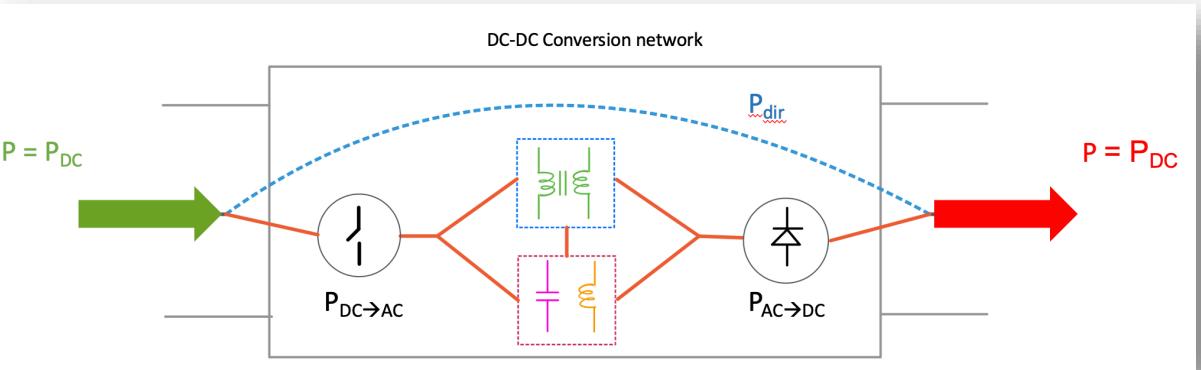

What is the optimum power topology & power devices

for high current applications?

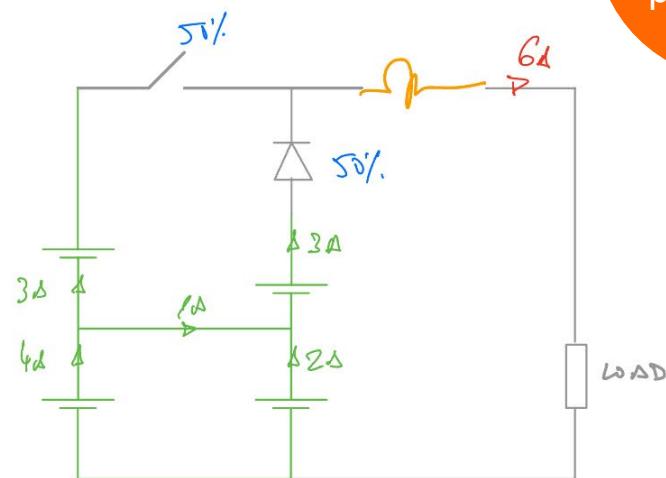

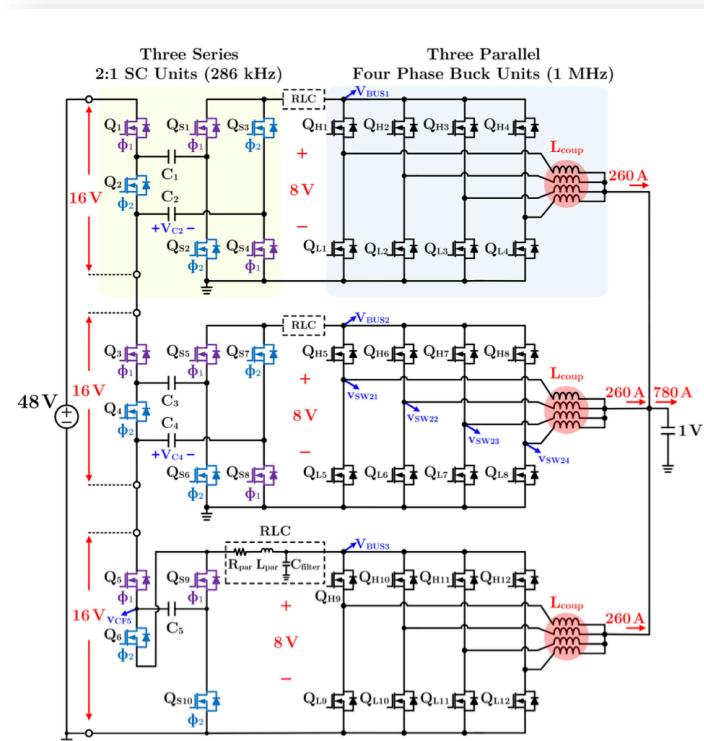

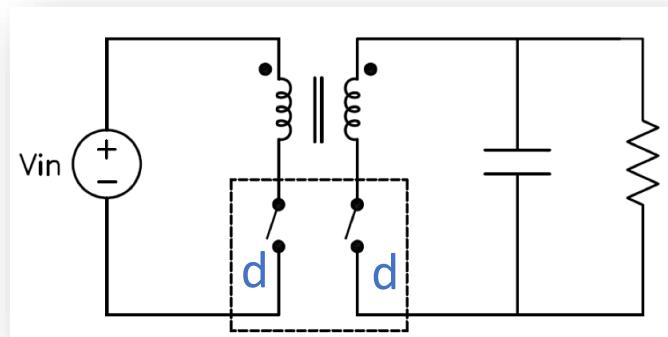

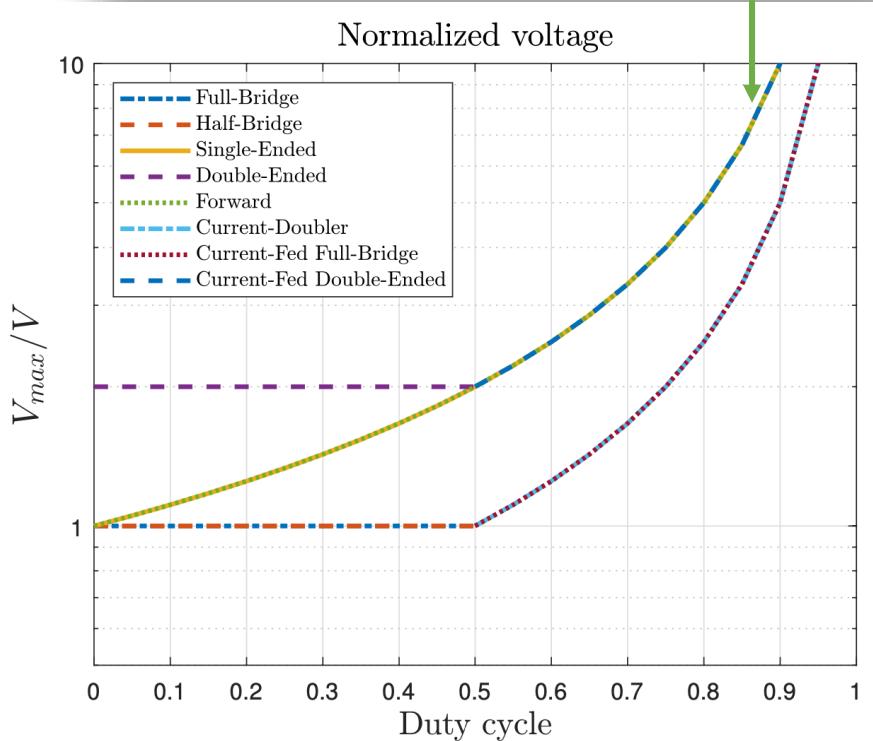

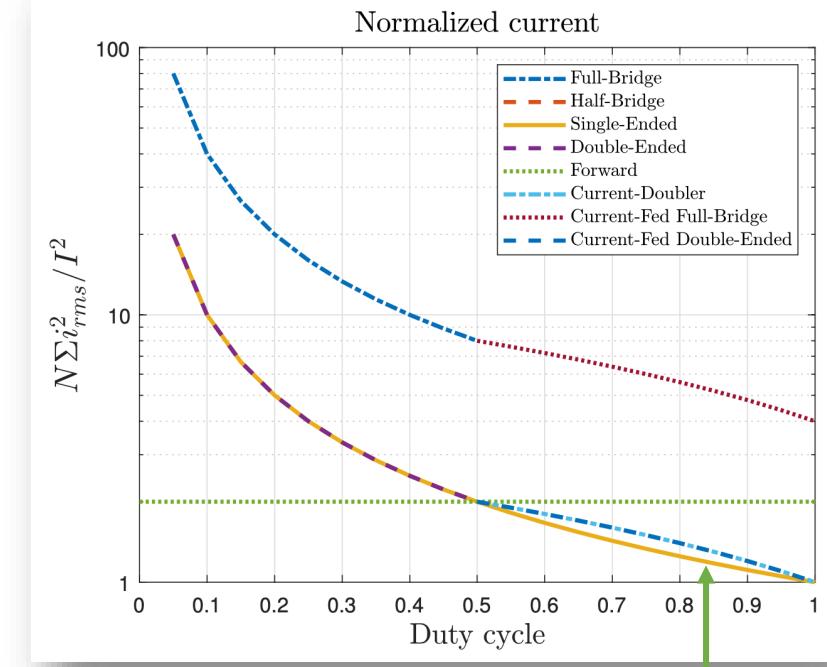

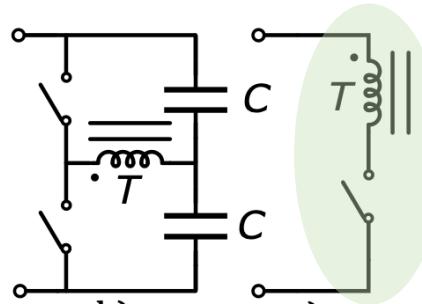

## #2 Use HV devices in LV applications

“i” impacts more than “v” on conduction loss

In 2023...

...in 2050

- 50% duty cycle

- 90% duty cycle

“**Low Voltage**” power switches

for **High Voltage** applications

“**High Voltage**” power switches

for **Low Voltage** applications

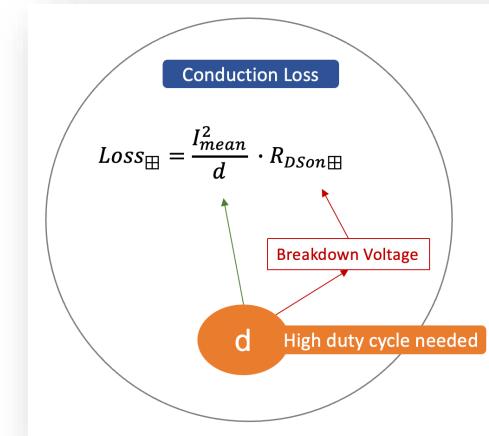

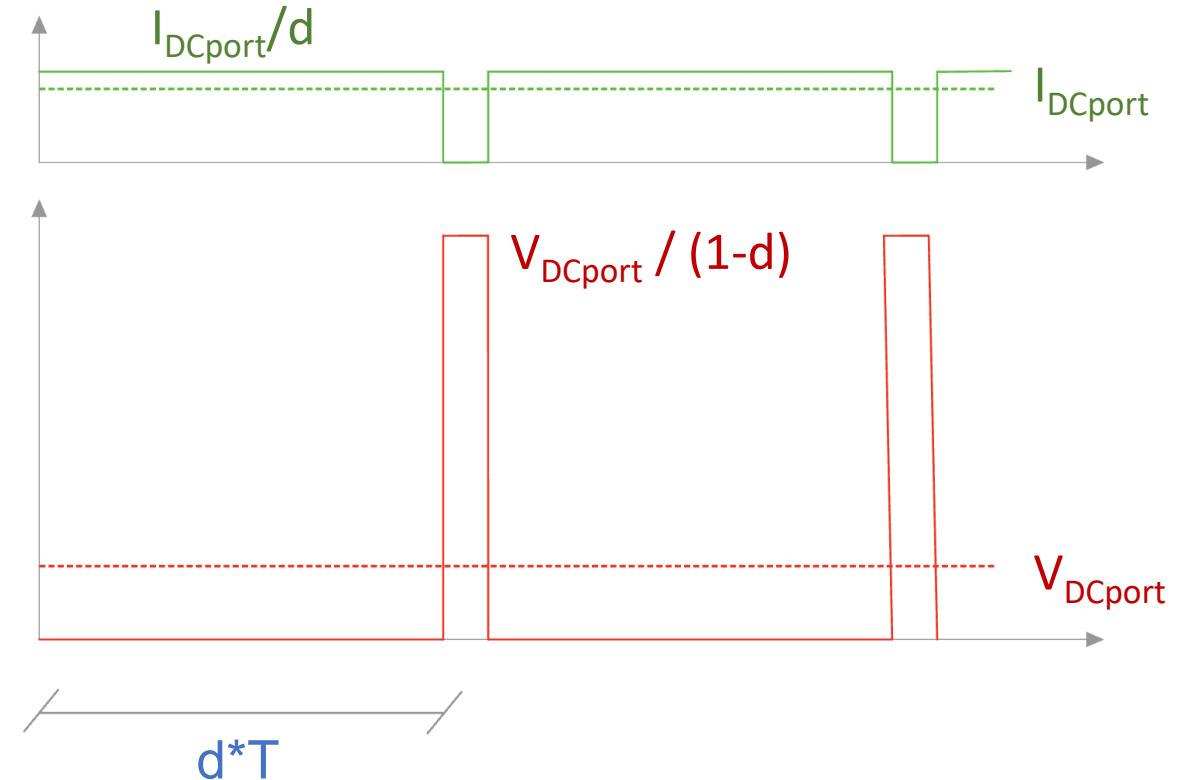

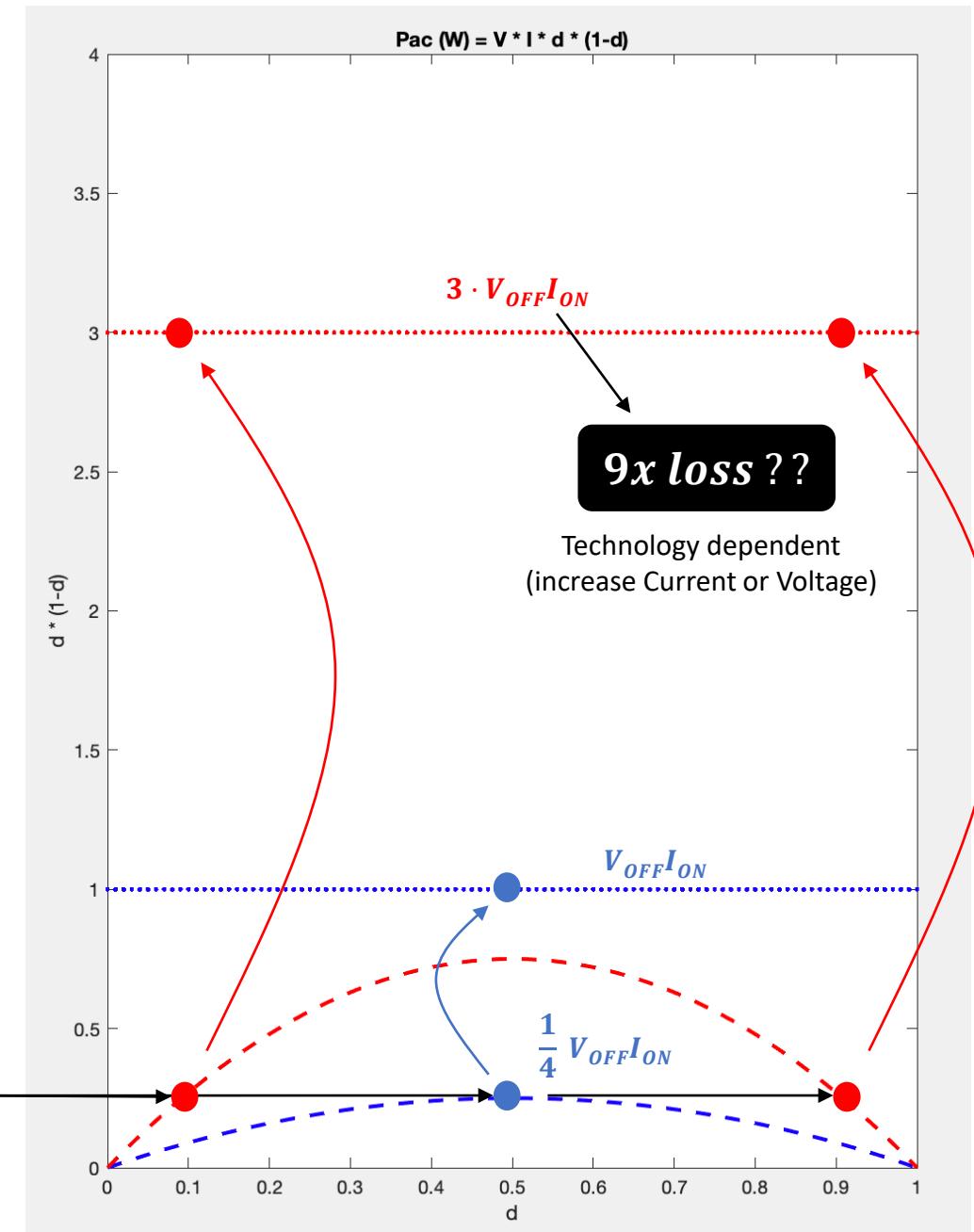

## #2 Use HV devices in LV applications

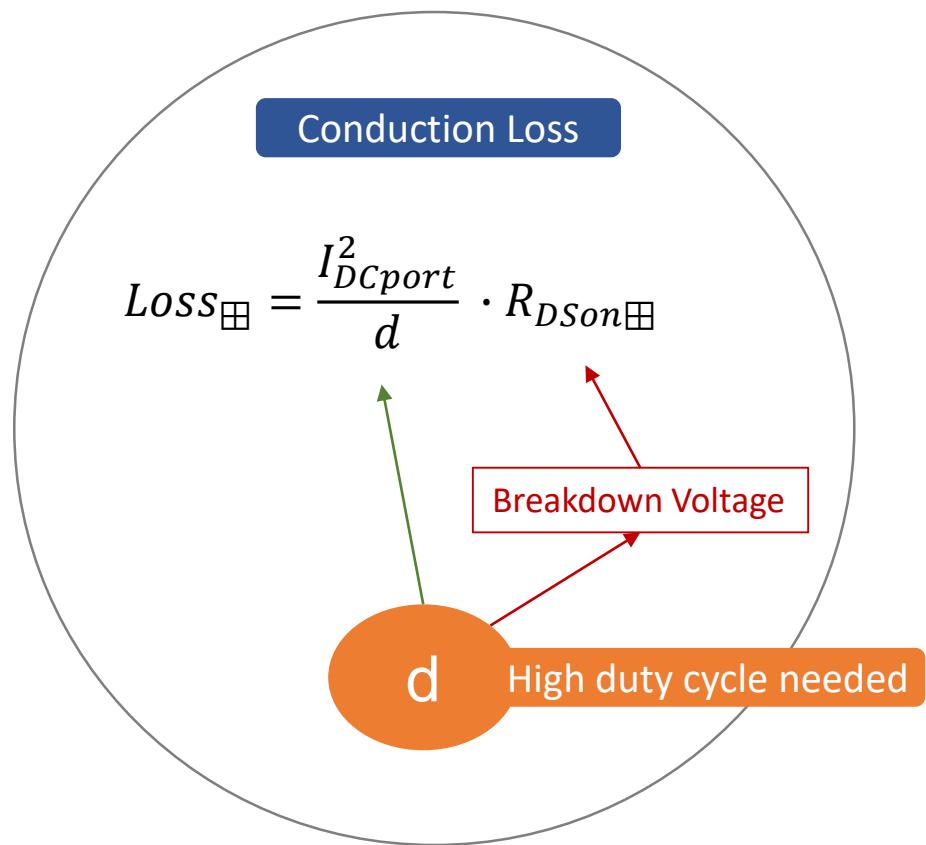

“i” impacts more than “v” on conduction loss

Optimize for

CONDUCTION LOSSES

$$i_{rms} = \frac{I_{DCport}}{\sqrt{d}} \rightarrow Loss_{\square} = \frac{I_{DCport}^2}{d} \cdot R_{DSon \square}$$

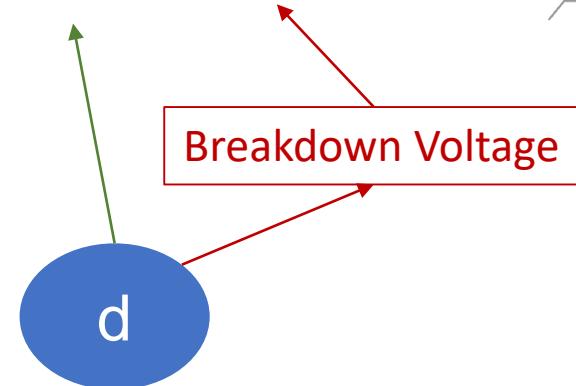

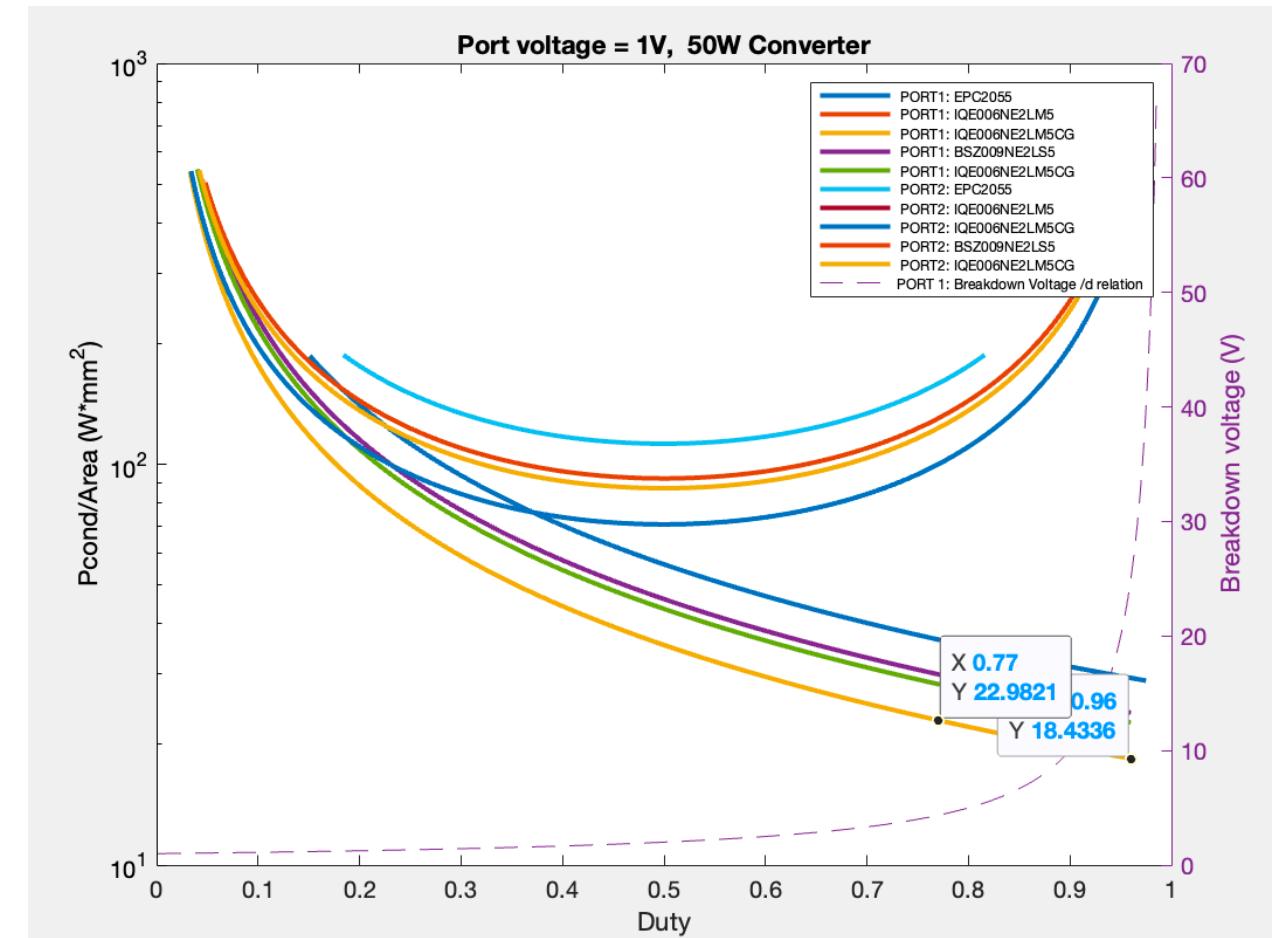

## #2 Use HV devices in LV applications

“i” impacts more than “v” on conduction loss

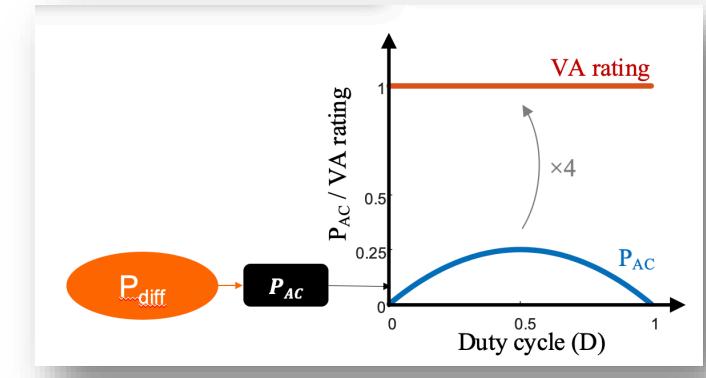

optimum “d” depends on

Semiconductor **TECHNOLOGY**

(Si, GaN, SiC)

## #2 Use HV devices in LV applications

“i” impacts more than “v” on conduction loss

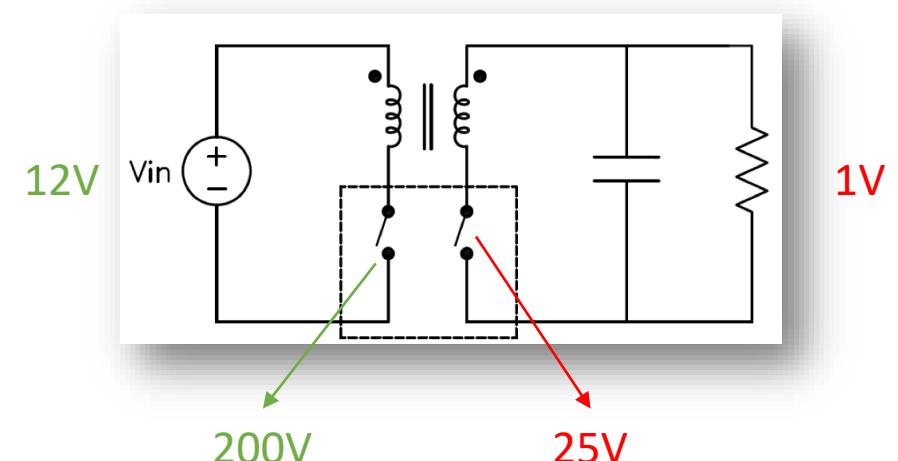

For 1V output

D=96%

25V devices

High Voltage - low  $R_{dson}$  power switches are needed for high current applications

## #2 Use HV devices in LV applications

“i” impacts more than “v” on conduction loss

Optimum “D”

50% ??

Apparently YES,

but NOT for low voltage, kA applications,

D= 90% is better !!

$P_{AC}$

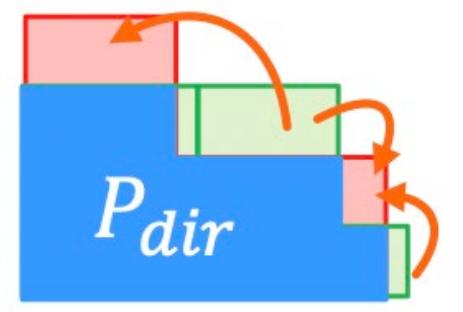

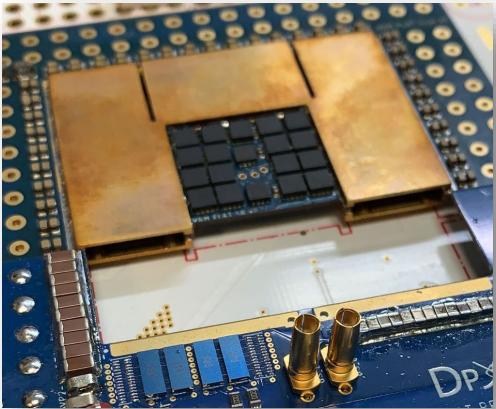

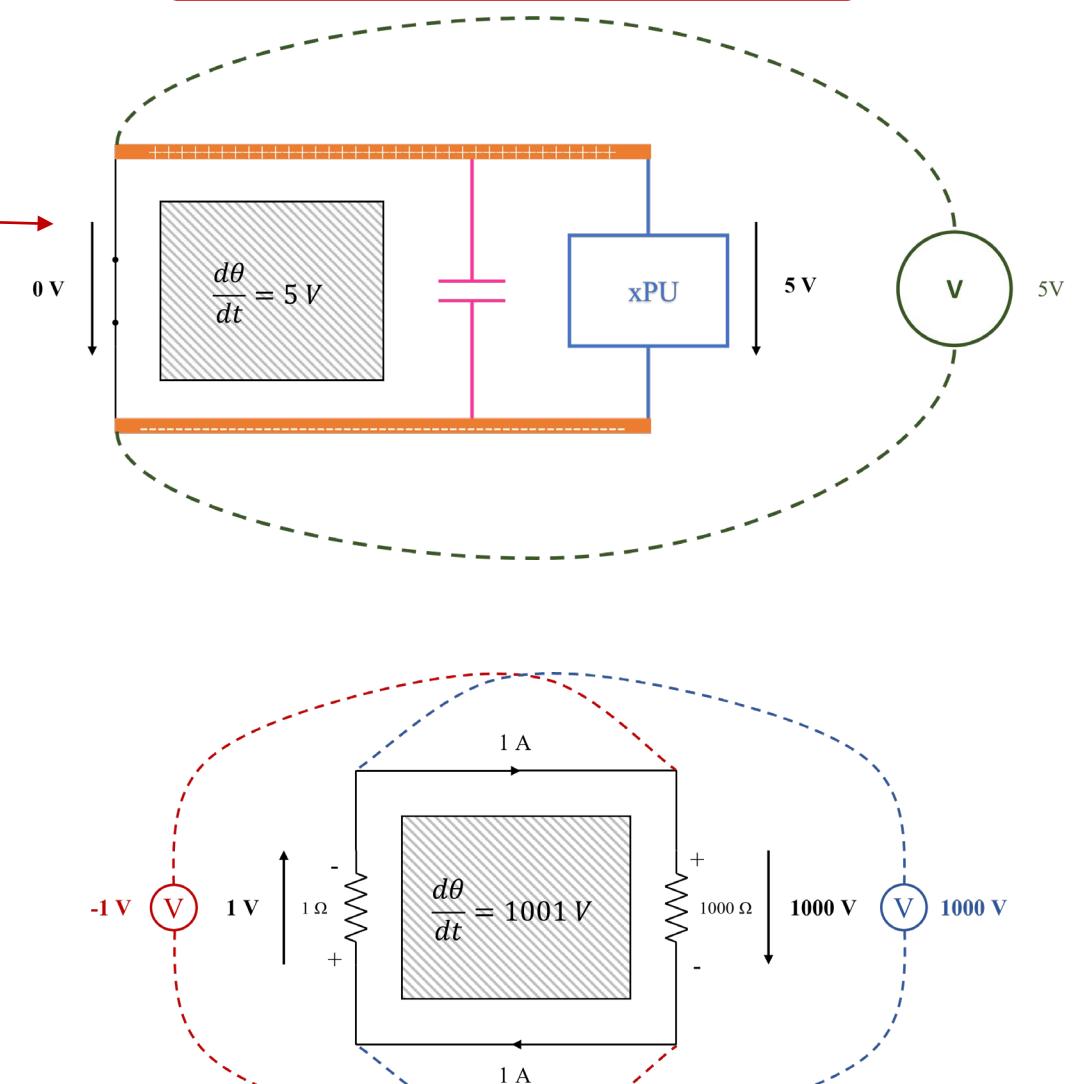

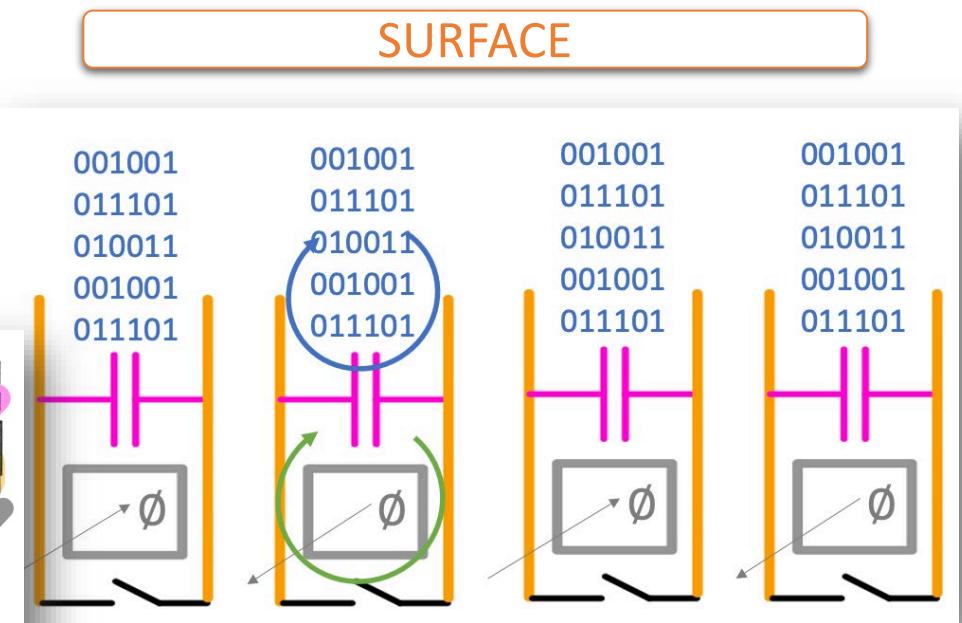

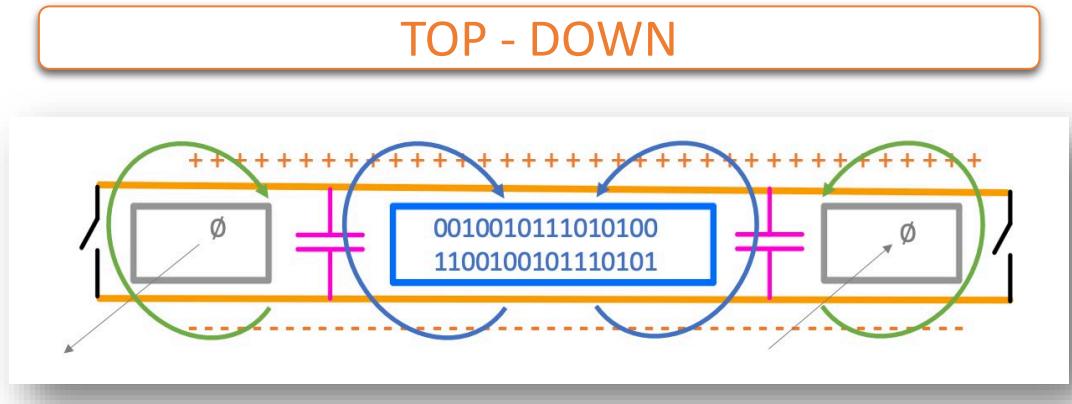

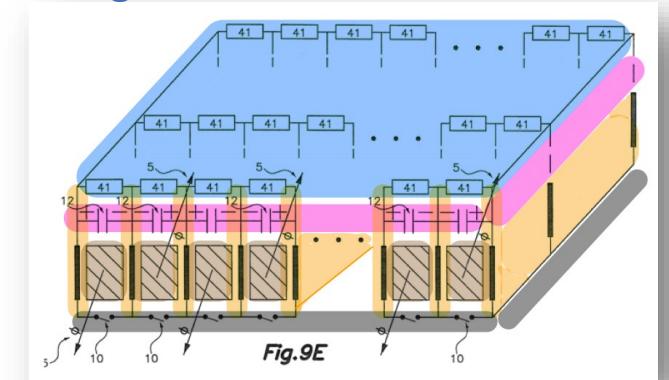

## #3 SURFACE power delivery

Generate LOAD current ubiquitously (Extension of “Point of Load”)

What is the optimum delivery path for high current applications?

# Minimize Conduction LOSS

Generate

load current

“locally”

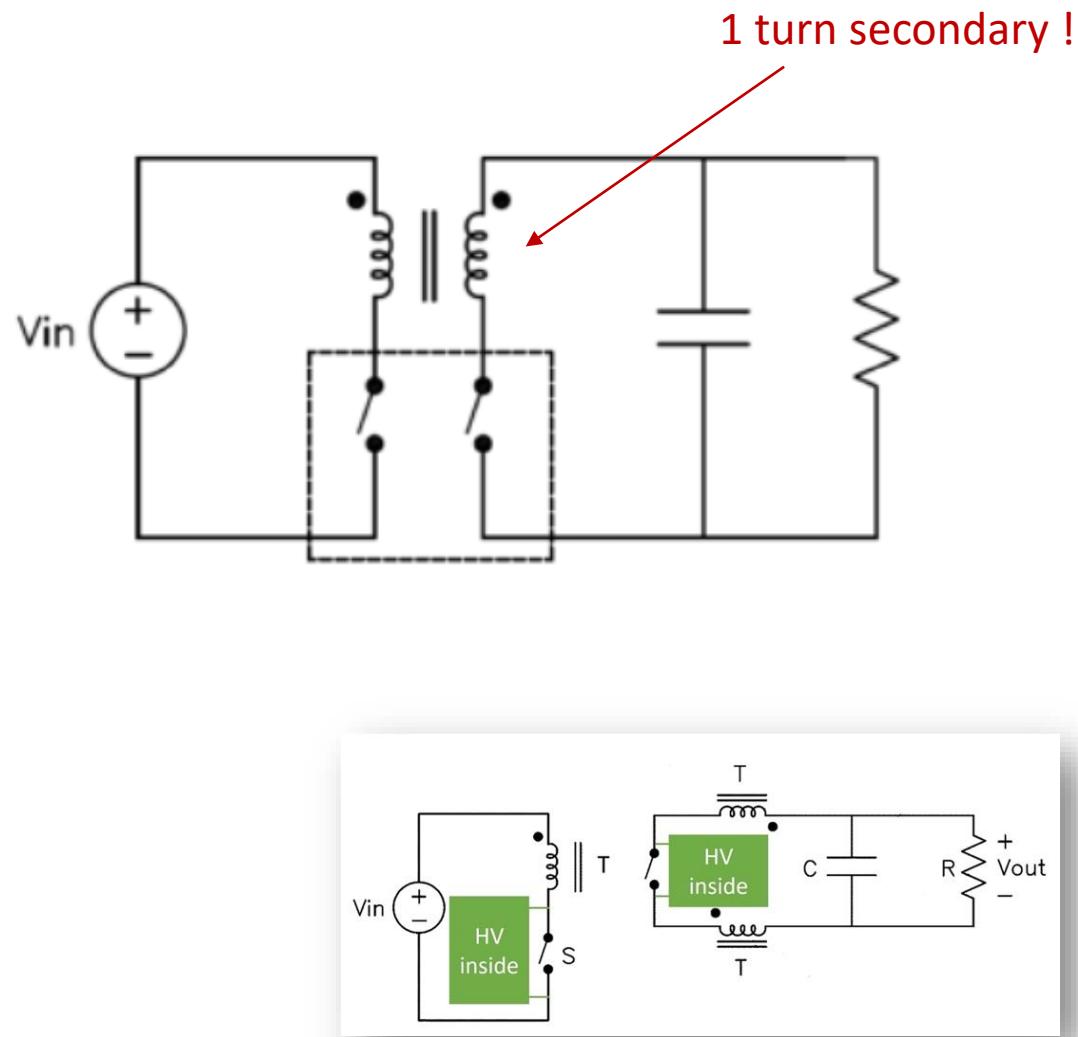

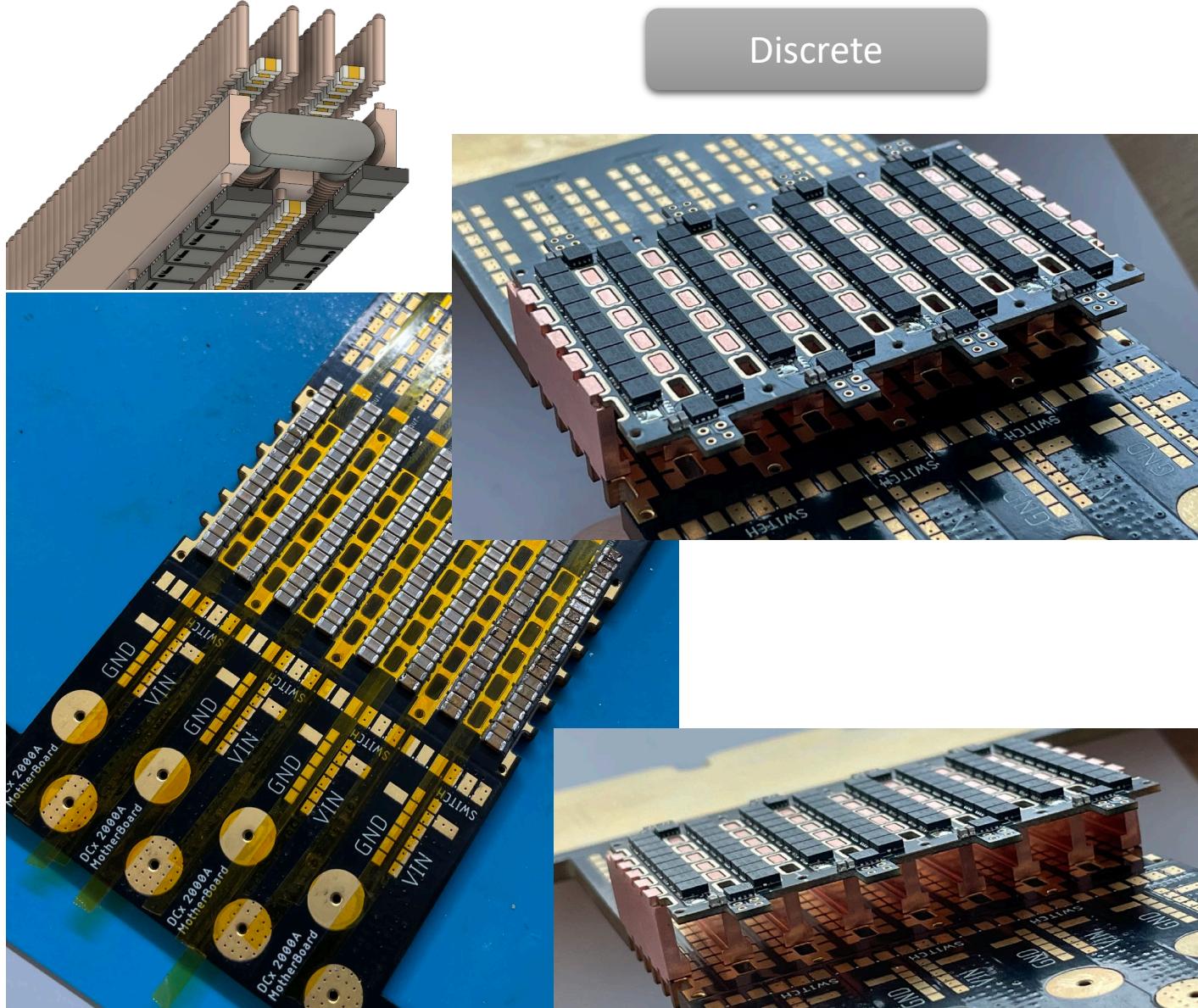

## #3 SURFACE power delivery

Generate LOAD current ubiquitously (Extension of “Point of Load”)

4 segments 1-turn winding

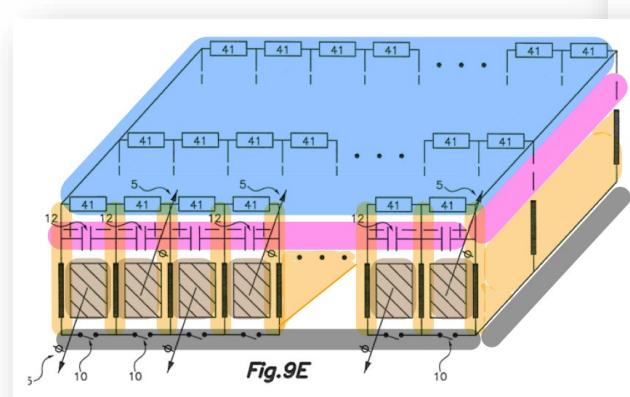

# #3 SURFACE power delivery

Generate LOAD current ubiquitously (Extension of “Point of Load”)

# #3 SURFACE power delivery

Generate LOAD current ubiquitously (Extension of “Point of Load”)

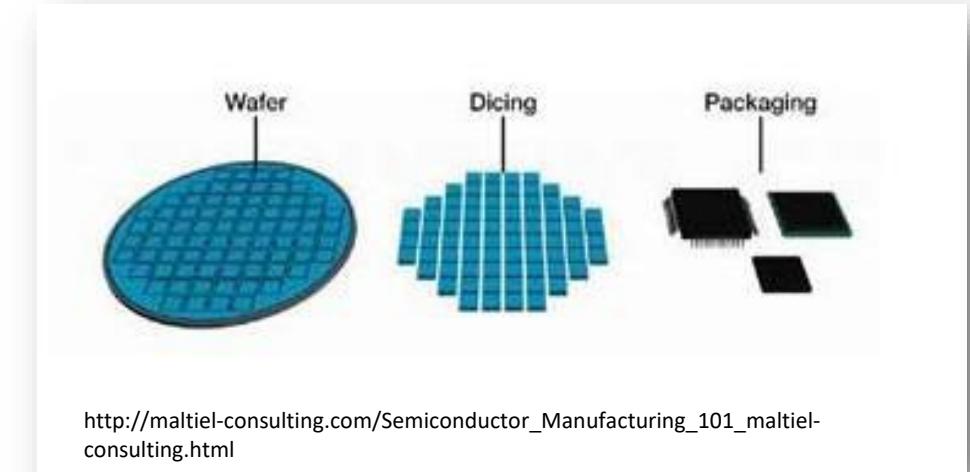

In 2023...

Discrete

...in 2050

Integrated

[http://maltiel-consulting.com/Semiconductor\\_Manufacturing\\_101\\_maltiel-consulting.html](http://maltiel-consulting.com/Semiconductor_Manufacturing_101_maltiel-consulting.html)

Power conversion is one more layer of the digital circuit

## Press headlines

In 2023...

...in 2050

Process Less power

## 1. RECONFIGURATION of Sources &amp; loads and SYNTHESIS of the power architecture:

- “supplied” power is calculated

- “stacking” sources or loads

- “processed” power is calculated

- “reconfiguration” sources & loads

- “synthesis” of power converters

High current (kA) applications requires lower CONDUCTION LOSS

## 2. HV voltage semiconductors, to reduce RMS current by high duty cycles

- 50% duty cycle

- FOM:  $R_{xq}$

- 90% duty cycle

- FOM:  $R_{xarea}$

## 3. Power Delivery: generate load current (kA) ubiquitously

- “Lateral” & “Vertical” power delivery

- “Rectifiers” based on semiconductors

- “Surface” power delivery

- “Faradays” paradox gets rid of the rectifiers